# 5 to 60V Three-Phase Brushless DC Motor Pre-Driver

#### **FEATURES**

- Wide Operating Voltage: 5V to 60V

- Charge Pump Gate Drive Supply

- 100% Duty Operation with Trickle Charge Circuit

- 1A Maximum Peak Source Current

- 2A Maximum Peak Sink Current

- 3.3V and 5V Logic Compatible

- Low-Power Sleep Mode

- Adjustable Dead-Time

- **Fault Indication Output**

- **Full Protection Features**

- Over Current Protection

- **Short Circuit Protection**

- Input Undervoltage Lockout

- Gate Driver Undervoltage Lockout

- Bootstrap Undervoltage Protection

- Thermal Shutdown Protection

- Available in QFN-28L(4mm×4mm) Package.

# **DESCRIPTION**

The SCT55610 is a highly integrated gate driver IC for three-phase Brushless DC(BLDC) motor control. It is capable of driving 3 high-side and 3 low-side N-channel MOSFETs with a wide input supply range from 5V to 60V.

The SCT55610 supports 100% duty operation with an internal trickle charge circuit to maintain high-side gate driver voltage. Low-power sleep mode is supported to achieve low stand-by current.

The SCT55610 provides full protection features, including over current protection, short circuit protection, input undervoltage lockout, gate driver undervoltage lockout. bootstrap undervoltage protection and thermal shutdown protection. Fault conditions are indicated through an open-drain output pin(nFAULT).

The device is available in 4mm×4mm QFN-28L package.

#### APPLICATIONS

- Three-Phase Brushless DC Motor

- Fans and Pumps

- Drone

- Robot Vacuum

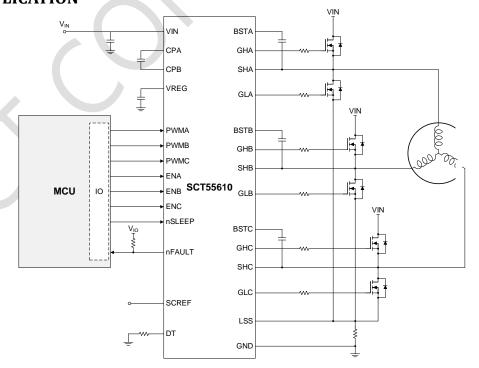

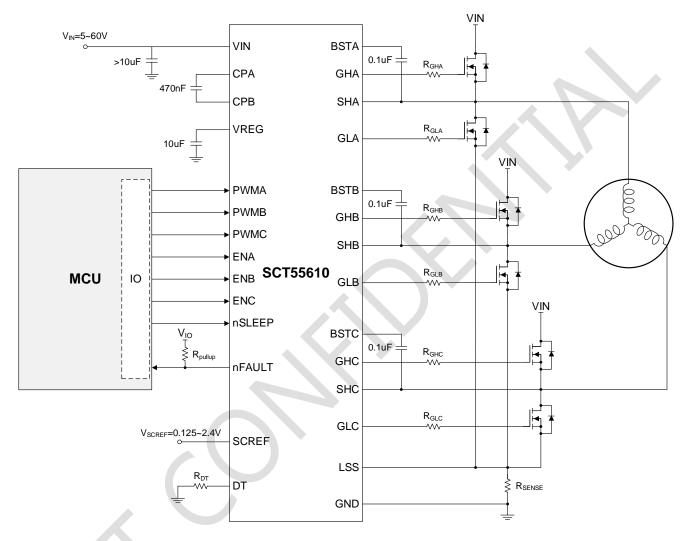

# TYPICAL APPLICATION

# **REVISION HISTORY**

Revision 0.8: Customer Sample.

Revision 0.81: Update Part Number, Electrical Characteristics and Application Waveforms.

### **DEVICE ORDER INFORMATION**

| PART NUMBER | PACKAGE MARKING | PACKAGE DISCRIPTION |

|-------------|-----------------|---------------------|

| SCT55610QZA | 5610            | QFN-28L             |

<sup>1)</sup> For Tape & Reel, Add Suffix R (e.g. SCT55610QZAR)

# ABSOLUTE MAXIMUM RATINGS

Over operating free-air temperature unless otherwise noted<sup>(1)</sup>

| DESCRIPTION                                                                            | MIN  | MAX | UNIT |

|----------------------------------------------------------------------------------------|------|-----|------|

| VIN                                                                                    | -0.3 | 65  | V    |

| CPA                                                                                    | -0.3 | 13  | V    |

| СРВ                                                                                    | -0.3 | 6   | V    |

| VREG                                                                                   | -0.3 | 13  | V    |

| BSTA - SHA, BSTB - SHB, BSTC - SHC                                                     | -0.3 | 13  | V    |

| GHA - SHA, GHB - SHB, GHC - SHC                                                        | -0.3 | 13  | V    |

| SHA, SHB, SHC                                                                          | -0.3 | 65  | V    |

| GLA, GLB, GLC                                                                          | -0.3 | 13  | V    |

| LSS                                                                                    | -0.3 | 1   | V    |

| ENA, ENB, ENC, PWMA, PWMB, PWMC, DT, SCREF, nSLEEP, nFAULT, ISN, ISP, ISO, CSREF, GAIN | -0.3 | 6   | V    |

| Operation junction temperature T <sub>J</sub> <sup>(2)</sup>                           | -40  | 150 | °C   |

| Storage temperature T <sub>STG</sub>                                                   | -65  | 150 | °C   |

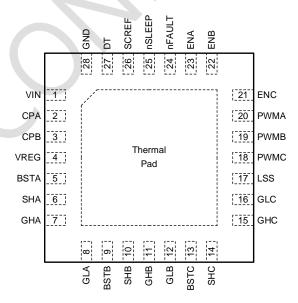

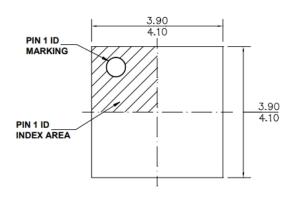

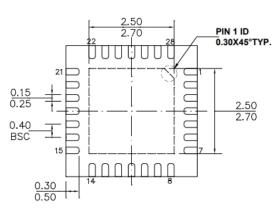

# PIN CONFIGURATION

Top View: 28-Lead QFN 4mm×4mm

<sup>(2)</sup> The IC includes thermal shutdown protection to protect the device during overload conditions. Junction temperature will exceed 150°C when thermal shutdown protection is active. Continuous operation above the specified maximum operating junction temperature will reduce lifetime.

For more information www.silicontent.com © 2024 Silicon Content Technology Co., Ltd. All Rights Reserved

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Rating may cause device permanent damage. The device is not guaranteed to function outside of its Recommended Operation Conditions.

# **PIN FUNCTIONS**

| NAME   | PIN | PIN FUNCTION                                                                                                                                         |

|--------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------|

| VIN    | 1   | Input supply voltage. Connect a bypass capacitor close to the pin.                                                                                   |

| СРА    | 2   | Charge nump quitching node. Connect a caramia conscitor between CDA and CDD                                                                          |

| СРВ    | 3   | Charge pump switching node. Connect a ceramic capacitor between CPA and CPB.                                                                         |

| VREG   | 4   | Gate driver supply output. Connect a ceramic capacitor to ground.                                                                                    |

| BSTA   | 5   | Phase A bootstrap pin. Connect a ceramic capacitor between BSTA and SHA.                                                                             |

| SHA    | 6   | Phase A high-side source pin. Connect to the source of high-side FET.                                                                                |

| GHA    | 7   | Phase A high-side gate driver output. Connect to the gate of high-side FET.                                                                          |

| GLA    | 8   | Phase A low-side gate driver output. Connect to the gate of low-side FET.                                                                            |

| BSTB   | 9   | Phase B bootstrap pin. Connect a ceramic capacitor between BSTB and SHB.                                                                             |

| SHB    | 10  | Phase B high-side source pin. Connect to the source of high-side FET.                                                                                |

| GHB    | 11  | Phase B high-side gate driver output. Connect to the gate of high-side FET.                                                                          |

| GLB    | 12  | Phase B low-side gate driver output. Connect to the gate of low-side FET.                                                                            |

| BSTC   | 13  | Phase C bootstrap pin. Connect a ceramic capacitor between BSTC and SHC.                                                                             |

| SHC    | 14  | Phase C high-side source pin. Connect to the source of high-side FET.                                                                                |

| GHC    | 15  | Phase C high-side gate driver output. Connect to the gate of high-side FET.                                                                          |

| GLC    | 16  | Phase C low-side gate driver output. Connect to the gate of low-side FET.                                                                            |

| LSS    | 17  | Low-side source pin. Connect to the sources of phase A/B/C low side FET.                                                                             |

| PWMC   | 18  | Phase C PWM signal input pin. Internal pulldown.                                                                                                     |

| PWMB   | 19  | Phase B PWM signal input pin. Internal pulldown.                                                                                                     |

| PWMA   | 20  | Phase A PWM signal input pin. Internal pulldown.                                                                                                     |

| ENC    | 21  | Phase C EN signal input pin. Internal pulldown.                                                                                                      |

| ENB    | 22  | Phase B EN signal input pin. Internal pulldown.                                                                                                      |

| ENA    | 23  | Phase A EN signal input pin. Internal pulldown.                                                                                                      |

| nFAULT | 24  | Fault indication output pin. Open-drain output and pulled low when in a fault condition. Connect an external pull-up resistor to an external supply. |

| nSLEEP | 25  | Sleep mode input pin. Logic low to enter low-power sleep mode and high to exit. Internal pulldown.                                                   |

| SCREF  | 26  | Short circuit protection reference input pin.                                                                                                        |

| DT     | 27  | Dead-time setting pin. Connect a resistor to ground to set the dead-time.                                                                            |

| GND    | 28  | Ground.                                                                                                                                              |

### RECOMMENDED OPERATING CONDITIONS

Over operating free-air temperature range unless otherwise noted

| PARAMETER          | DEFINITION                     | MIN   | MAX | UNIT |

|--------------------|--------------------------------|-------|-----|------|

| V <sub>IN</sub>    | Input voltage range            | 5     | 60  | V    |

| V <sub>SCREF</sub> | SCREF voltage                  | 0.125 | 2.4 | V    |

| TJ                 | Operating junction temperature | -40   | 125 | °C   |

### **ESD RATINGS**

| PARAMETER | DEFINITION                                                                                   | MIN  | MAX  | UNIT |

|-----------|----------------------------------------------------------------------------------------------|------|------|------|

| Vesd      | Human Body Model(HBM), per ANSI-JEDEC-JS-001-2014 specification, all pins <sup>(1)</sup>     | -1.5 | +1.5 | kV   |

| VESD      | Charged Device Model(CDM), per ANSI-JEDEC-JS-002-2014 specification, all pins <sup>(2)</sup> | -1   | +1   | kV   |

<sup>(1)</sup> JEDEC document JEP155 states that 500V HBM allows safe manufacturing with a standard ESD control process.

### THERMAL INFORMATION

| PARAMETER              | THERMAL METRIC                                              | QFN-28L | UNIT |

|------------------------|-------------------------------------------------------------|---------|------|

| Reja                   | Junction to ambient thermal resistance <sup>(1)</sup>       | 39.9    |      |

| R <sub>θJC (top)</sub> | Junction to case (top) thermal resistance <sup>(1)</sup>    | 44.85   |      |

| RθJC (bot)             | Junction to case (bottom) thermal resistance <sup>(1)</sup> | 6.6     | °C/W |

| Rejb                   | Junction to board thermal resistance <sup>(1)</sup>         | 18.15   |      |

| R <sub>ψJT</sub>       | Junction-to-top characterization parameter                  | 5.05    |      |

<sup>(1)</sup> SCT provides  $R_{\theta JA}$  and  $R_{\theta JC}$  numbers only as reference to estimate junction temperatures of the devices.  $R_{\theta JA}$  and  $R_{\theta JC}$  are not a characteristic of package itself, but of many other system level characteristics such as the design and layout of the printed circuit board (PCB) on which the SCT55610 is mounted, thermal pad size, and external environmental factors. The PCB board is a heat sink that is soldered to the leads and thermal pad of the SCT55610. Changing the design or configuration of the PCB board changes the efficiency of the heat sink and therefore the actual  $R_{\theta JA}$  and  $R_{\theta JC}$ .

# **ELECTRICAL CHARACTERISTICS**

Typical values correspond to V<sub>IN</sub> = 24V, T<sub>A</sub> = 25°C, unless otherwise stated.

| SYMBOL             | PARAMETER                     | TEST CONDITION                 | MIN | TYP | MAX | UNIT |  |  |

|--------------------|-------------------------------|--------------------------------|-----|-----|-----|------|--|--|

| Power Su           | Power Supply                  |                                |     |     |     |      |  |  |

| VIN                | Input Supply Voltage          |                                | 5   |     | 60  | ٧    |  |  |

| la                 | 10.                           | nSLEEP = 1, gate not switching |     | 1   | 2   | mA   |  |  |

| ISLEEP             | Quiescent Current             | nSLEEP = 0                     |     |     | 1   | uA   |  |  |

| Control Lo         | Control Logic                 |                                |     |     |     |      |  |  |

| VIL                | Input Logic Low Threshold     |                                |     |     | 0.8 | V    |  |  |

| VIH                | Input Logic High Threshold    |                                | 2   |     |     | V    |  |  |

| I <sub>IN(H)</sub> | La sia lanut Cumant           | V <sub>IH</sub> =5V            | -20 |     | 20  | uA   |  |  |

| I <sub>IN(L)</sub> | Logic Input Current           | V <sub>IL</sub> =0.8V          | -20 |     | 20  | uA   |  |  |

| ISLEEP-PD          | nSLEEP Pull-down Current      |                                |     | 1   |     | uA   |  |  |

| R <sub>PD</sub>    | Internal Pull-down Resistance | All logic inputs except nSLEEP |     | 820 |     | kΩ   |  |  |

4 For more information www.silicontent.com © 2024 Silicon Content Technology Co., Ltd. All Rights Reserved

<sup>(2)</sup> JEDEC document JEP157 states that 250V CDM allows safe manufacturing with a standard ESD control process.

| SYMBOL                | PARAMETER                          | TEST CONDITION                                 | MIN  | TYP  | MAX  | UNIT |

|-----------------------|------------------------------------|------------------------------------------------|------|------|------|------|

| nFAULT O              | Output (Open-Drain Output)         | ,                                              | •    |      |      | 1    |

| VoL                   | Output low voltage                 | Io=5mA                                         |      |      | 0.5  | V    |

| Іон                   | Output high leakage current        | Vo=3.3V                                        |      |      | 1    | uA   |

| Protection            | n Circuits                         |                                                |      |      |      |      |

| V <sub>IN_RISE</sub>  | VIN UVLO Rising Threshold          |                                                |      | 4.2  | 4.5  | V    |

| V <sub>IN_HYS</sub>   | VIN UVLO Hysteresis                |                                                |      | 200  |      | mV   |

| V <sub>REG_RISE</sub> | VREG UVLO Rising Threshold         |                                                |      | 7.6  |      | ٧    |

| V <sub>REG_HYS</sub>  | VREG UVLO Hysteresis               |                                                |      | 1.6  |      | V    |

| 1.7                   | Short-Circuit Threshold Accuracy   | V <sub>SCREF</sub> =1V, T <sub>J</sub> =25°C   | 0.8  | 1    | 1.2  | V    |

| Vsc                   | (MOSFET V <sub>DS</sub> )          | V <sub>SCREF</sub> =2.4V, T <sub>J</sub> =25°C | 2.18 | 2.4  | 2.62 | V    |

| toc                   | OCP Deglitch Time                  |                                                |      | 3    |      | us   |

| t <sub>SLEEP</sub>    | SLEEP Wakeup Time                  | VREG cap=10uF                                  |      | 250  |      | us   |

| V <sub>LSS-OCP</sub>  | LSS OCP threshold                  |                                                | 0.4  | 0.5  | 0.6  | V    |

| T <sub>TSD</sub>      | Thermal Shutdown                   |                                                |      | 150  |      | °C   |

| V <sub>BSTUV</sub>    | BSTx-SWx Falling Threshold         |                                                |      | 4.3  |      | V    |

| Gate Drive            | er                                 |                                                |      |      |      |      |

| V <sub>FBOOT</sub>    | Bootstrap Diode Forward Voltage    | I <sub>D</sub> =10mA                           |      | 1    |      | V    |

| \ /                   | VDEO Output Vallage                | V <sub>IN</sub> =6~60V                         | 10.5 | 11.3 | 12   | V    |

| $V_{REG}$             | VREG Output Voltage                | V <sub>IN</sub> =5~6V                          | 9    |      |      | V    |

| loso                  | Maximum source current             |                                                |      | 1    |      | Α    |

| losi                  | Maximum sink current               |                                                |      | 2    |      | Α    |

| R <sub>UP</sub>       | Gate drive pull-up resistance      | V <sub>DS</sub> =1V                            |      | 6    |      | Ω    |

| R <sub>HS_DN</sub>    | HS gate drive pull-down resistance | V <sub>DS</sub> =1V                            | 0.2  |      | 3    | Ω    |

| R <sub>LS_DN</sub>    | LS gate drive pull-down resistance | V <sub>DS</sub> =1V                            | 1    |      | 2.5  | Ω    |

| tLS                   | LS automatic turn-on time          | At ENx rising edge                             |      | 2    |      | us   |

| f <sub>CP</sub>       | Charge pump frequency              |                                                |      | 110  |      | kHz  |

|                       |                                    | DT open                                        |      | 5    |      | us   |

| tDEAD                 | Dead Time                          | R <sub>DT</sub> =200kΩ                         |      | 0.74 |      | us   |

|                       |                                    | DT tied to GND                                 |      | 30   |      | ns   |

# TYPICAL CHARACTERISTICS

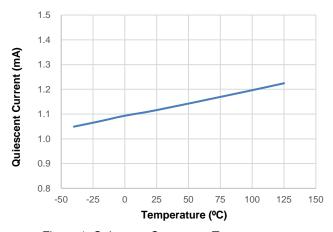

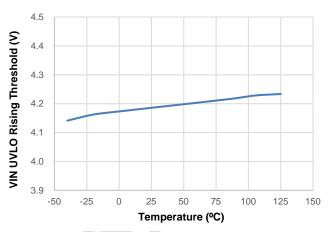

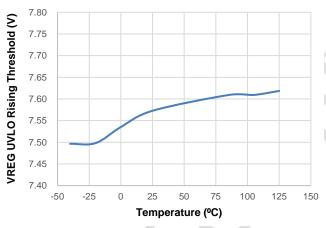

$V_{IN} = 24V$ ,  $T_A = 25$ °C, unless otherwise noted.

Figure 1. Quiescent Current vs. Temperature

Figure 2. VIN UVLO Rising vs. Temperature

Figure 3. VREG UVLO Rising vs. Temperature

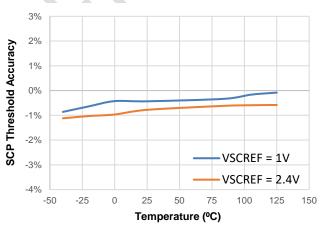

Figure 4. SCP Threshold Accuracy vs. Temperature

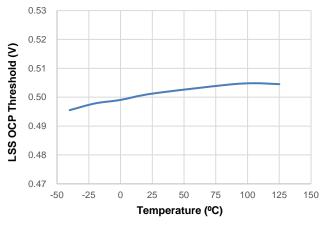

Figure 5. LSS OCP Threshold vs. Temperature

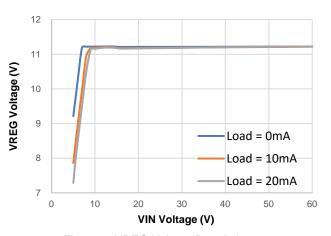

Figure 6. VREG Voltage Regulation

# **FUNCTIONAL BLOCK DIAGRAM**

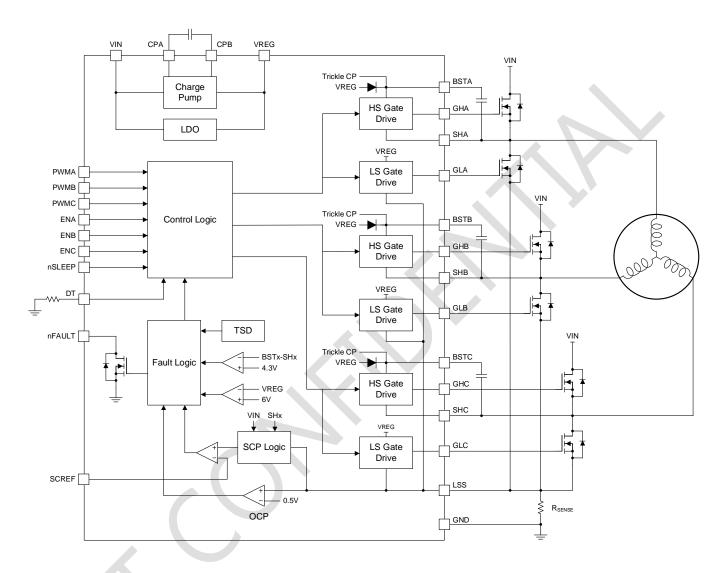

Figure 7. Functional Block Diagram

### **OPERATION**

#### Overview

The SCT55610 is a highly integrated gate driver IC designed for three-phase Brushless DC(BLDC) motor control with the ability to drive three high-side and three low-side N-channel MOSFETs. Each channel can source up to 1A peak current and sink up to 2A peak current, with flexible dead time configuration by an external resistor. It uses a charge pump to generate the gate drive power to operate over a wide input voltage range from 5V to 60V. It also supports 100% duty operation with an internal trickle charge circuit to maintain high-side gate driver voltage. Low-power sleep mode is supported to achieve low stand-by current.

The SCT55610 provides full protection features, including over current protection, short circuit protection, input undervoltage lockout, gate driver undervoltage lockout, bootstrap undervoltage protection and thermal shutdown protection to timely shut down and properly protect the system from various failures. Meanwhile, these fault conditions are indicated through an open-drain output pin, nFAULT, for real-time monitoring and warning.

#### 3-Phase Gate Drive

The SCT55610 consists of 3 half-bridge gate drivers (phase A, B, C), which could be used in combination to implement 3-phase motor control, or used separately for any other application. The gate drive power is supplied from VREG, which is regulated at around 11V and generated from an internal charge pump when VIN is low, and from an internal LDO when VIN is high enough. A 10uF ceramic capacitor close to VREG pin and a 470nF ceramic capacitor between CPA and CPB pins are suggested to stabilize the gate drive power for most applications.

An internal trickle charge pump is integrated to support 100% duty operation, where the high-side MOSFET keeps on and the trickle charge circuit provides a small current to balance the leakage on the BSTx node.

All the gate driver outputs have an internal pulldown which is activated when the SCT55610 is shut down or in sleep mode to prevent unexpected turning-on of MOSFETs. After it is back to normal operation, the internal pulldown is disabled.

#### **Input Logic**

The SCT55610 generates the gate drive outputs based on the input logic signals at ENx and PWMx pins. ENx and PWMx pins have internal pulldown to avoid noise when floating. Refer to Table 1 for the truth table.

|     |      | Y   |     |      |

|-----|------|-----|-----|------|

| ENx | PWMx | GHx | GLx | SHx  |

| 0   | X    | L   | L   | Hi-Z |

| 1   | 1    | Н   | L   | VIN  |

| 1   | 0    | L   | Н   | GND  |

Table 1. Input Logic Truth Table

# **Dead Time Adjustment**

The DT pin configures the gate drive dead time with an external resistor connected to ground. The dead time could be calculated with Equation (1):

$$t_{dead}(ns) = 3.7 \times R_{DT}(k\Omega) \tag{1}$$

If DT pin is directly tied to ground, a minimum dead time of around 30ns will be applied. If DT pin is left floating, a maximum dead time of around 5us will be applied.

# **Low-side Automatic Turn-on**

To ensure enough bootstrap voltage before operation, each time ENx pin receives a rising edge from low to high, the corresponding GLx will automatically output high to turn on the low-side MOSFET for around 2us, where SHx is connected to ground and the bootstrap capacitor is charged by VREG. This action always occurs regardless of PWMx state.

#### Sleep Mode

The SCT55610 can enter a low-power sleep mode where most internal circuits are turned off to save power. All the gate drivers are disabled in sleep mode. The sleep mode is entered by pulling nSLEEP pin low, and exited by pulling nSLEEP pin high with a wakeup delay of around 250us. The nSLEEP pin has an internal pulldown so it must be pulled high for normal operation.

#### **Over Current Protection**

The SCT55610 protects the system from over-current failure by monitoring LSS pin voltage and timely shutting down when it is over 0.5V. The LSS pin is connected to the sources of the three low-side MOSFETs, and tied to ground through an external sense resistor, whose voltage drop equals the resistance multiplied by the total current of the three phases. For example, if a  $50m\Omega$  sense resistor is used, the over current protection will be triggered once the total current exceeds 10A. When an over-current condition is detected for over 3us deglitch time, all the gate driver outputs are driven low immediately and nFAULT pin is pulled low. The SCT55610 will be latched in the fault state even after the over-current condition is gone, and only reset by toggling nSLEEP pin or power cycle.

Over current protection can be disabled by connecting LSS pin directly to ground or connecting SCREF pin to VREG through a  $100k\Omega$  resistor.

#### **Short Circuit Protection**

The SCT55610 protects the system from short-circuit failure by monitoring the drain-to-source voltage drop of the turned-on MOSFET through VIN, SHx and LSS pins. In a short-circuit case, the current running through the MOSFET immediately increases and so does the voltage across the MOSFET. When a voltage drop higher than the short-circuit threshold is detected for over 3us deglitch time, all the gate driver outputs are driven low immediately and nFAULT pin is pulled low. The short-circuit threshold is set by SCREF pin with an external voltage reference. The SCT55610 will be latched in the fault state even after the short-circuit condition is gone, and only reset by toggling nSLEEP pin or power cycle.

Short circuit protection can be disabled by connecting SCREF pin to VREG through a  $100k\Omega$  resistor.

#### **Undervoltage Lockout Protection**

The SCT55610 monitors VIN, VREG and bootstrap voltage and shuts down when any of them falls lower than its undervoltage lockout threshold. In these cases, the SCT55610 will pull all gate driver outputs low immediately, latched in the fault state and only reset by toggling nSLEEP pin or power cycle. See Electrical Characteristics table for detailed undervoltage lockout thresholds.

#### **Thermal Shutdown**

Once the junction temperature of SCT55610 exceeds 150°C, the thermal sensing circuit shuts down the device. All the gate driver outputs are driven low immediately and nFAULT pin is pulled low. The SCT55610 will be latched in the fault state even after the over-temperature condition is gone, and only reset by toggling nSLEEP pin or power cycle. Thermal shutdown prevents the damage on device during excessive heat and power dissipation condition.

# **Fault Action and Response**

The fault action and response of SCT55610 are listed in Table 2.

Table 2. Fault Action and Response

| Fault            | Condition                        | Report | Gate Driver | Recovery               |

|------------------|----------------------------------|--------|-------------|------------------------|

| VIN UVLO         | $V_{IN} < 4V$                    | None   | Pulled low  | V <sub>IN</sub> > 4.2V |

| VREG UVLO        | V <sub>REG</sub> < 6V            | nFAULT | Pulled low  | Latched                |

| BST UVLO         | BSTx - SWx < 4.3V<br>and ENx = 1 | nFAULT | Pulled low  | Latched                |

| Over-current     | V <sub>LSS</sub> > 0.5V          | nFAULT | Pulled low  | Latched                |

| Short-circuit    | Vds_on > Vscref                  | nFAULT | Pulled low  | Latched                |

| Thermal Shutdown | T <sub>J</sub> > 150°C           | nFAULT | Pulled low  | Latched                |

For more information www.silicontent.com © 2024 Silicon Content Technology Co., Ltd. All Rights Reserved 9

# APPLICATION INFORMATION

# **Typical Application**

Figure 8. Three-Phase BLDC Motor Driver

#### **Driver Power Dissipation**

Generally, the power dissipation in the SCT55610 depends on the driver-stage loss and VREG regulation loss.

The power loss of a single gate driver can be estimated by Equation (2):

$$P_{Gtdrv} = Q_g \times V_{REG} \times f_{sw} \tag{2}$$

where

- Qg is the total gate charge of the power device

- f<sub>SW</sub> is the switching frequency

- V<sub>REG</sub> is the gate drive voltage

If the gate resistor R<sub>G</sub> applied between the driver output and gate of power device to slow down the switching transition, the power loss of a single gate driver can be estimated by Equation (3):

$$P_{Gtdrv} = \frac{1}{2} \times Q_g \times V_{REG} \times f_{sw} \times \left(\frac{R_{UP}}{R_{UP} + R_G} + \frac{R_{DN}}{R_{DN} + R_G}\right)$$

(3)

where

- Rup is the gate driver pull-up resistance

- R<sub>DN</sub> is the gate driver pull-down resistance

- R<sub>G</sub> is the external resistance between the driver output and gate of power device

For a typical three-phase BLDC motor control, always only one of the three half-bridges are switching at fsw during the whole rotation cycle. In this case, the total driver-stage power dissipation can be estimated by one half-bridge, namely a high-side gate driver and a low-side gate driver.

The gate drive voltage V<sub>REG</sub> is generated from VIN through either a charge pump when VIN is low or a LDO when VIN is high. The power loss of V<sub>REG</sub> regulation can be estimated referring to Table 3:

Input Range Mode  $P_{REG} = \left(2 \times \frac{V_{IN}}{V_{REG}} - 1\right) \times P_{Gtdrv\_total}$   $P_{REG} = \left(\frac{V_{IN}}{V_{REG}} - 1\right) \times P_{Gtdrv\_total}$ VIN < 16V Charge Pump VIN > 16V LDO

Table 3 V<sub>REG</sub> Regulation Loss

# **Thermal Considerations**

The maximum IC junction temperature should be restricted to 125°C under normal operating conditions. Calculate the maximum allowable dissipation, P<sub>D(max)</sub>, and keep the actual power dissipation less than or equal to P<sub>D(max)</sub>. The maximum-power-dissipation limit is determined using Equation (4):

$$P_{D(MAX)} = \frac{125 - T_A}{R_{\theta \mid A}} \tag{4}$$

where

- T<sub>A</sub> is the maximum ambient temperature for the application

- R<sub>BJA</sub> is the junction-to-ambient thermal resistance given in the Thermal Information table

The real junction-to-ambient thermal resistance Reja of the package greatly depends on the PCB type, layout, and environmental factor. Soldering the ground pin to a large ground plate enhance the thermal performance. Using more vias connects the ground plate on the top layer and bottom layer around the IC without solder mask also improves the thermal capability.

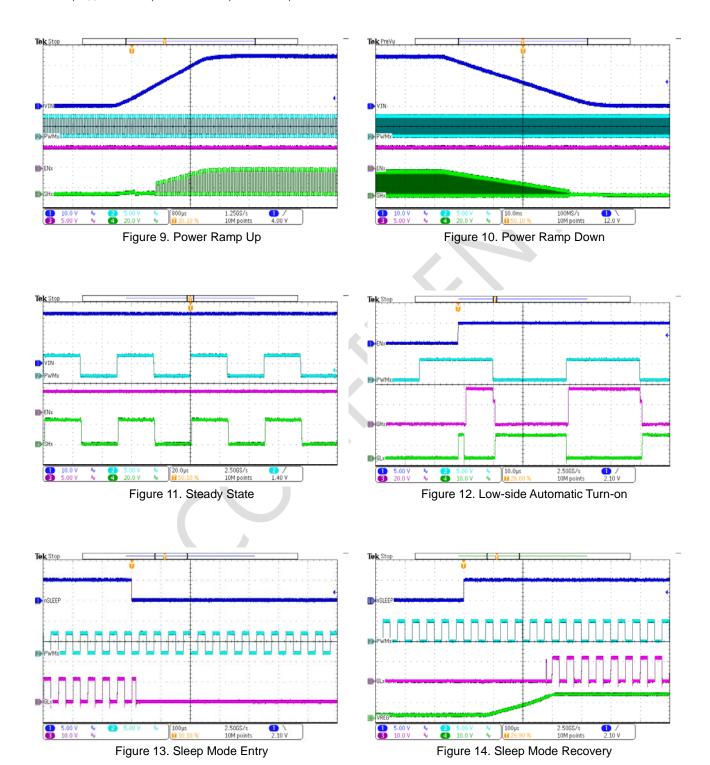

# **Application Waveforms**

$V_{IN} = 24V$ ,  $V_{SCREF} = 0.5V$ ,  $f_{PWM} = 20kHz$ ,  $T_A = 25$ °C, unless otherwise noted.

### **Layout Guideline**

The SCT55610 provides high output driving current and features very short rising and falling time at the gate of power device. The high di/dt might cause driver output unexpected ringing when the driver output loop is not designed well. The system could suffer from malfunction and EMI noise problems if the power device gate has serious ringing. For better performance, follow the layout guidelines as shown below.

- 1. Put the SCT55610 as close as possible to the power device to minimize the gate driving loop including the driver output and power device gate.

- 2. Place the power supply decoupling capacitors as close as possible to the VIN pin. Low-ESR ceramic capacitors of type X5R or X7R are recommended.

- 3. Place the VREG capacitor close to VREG pin.

- 4. Place the charge pump capacitor close to CPA and CPB pins with minimized loop.

- 5. Place the bootstrap capacitors close to BSTx and SHx pins with minimized loop.

- 6. For the low-side sense resistor for over current protection, it is recommended to use a wide-package resistor or paralleled resistors to minimize the parasitic inductance introduced between the LSS pin and ground.

- 7. At least one ground plane is recommended to provide noise shielding and thermal dissipation. The device thermal pad should be soldered to the top-layer ground plane with multiply vias connected to the bottom-layer ground plane to achieve better thermal performance.

For more information www.silicontent.com © 2024 Silicon Content Technology Co., Ltd. All Rights Reserved 13

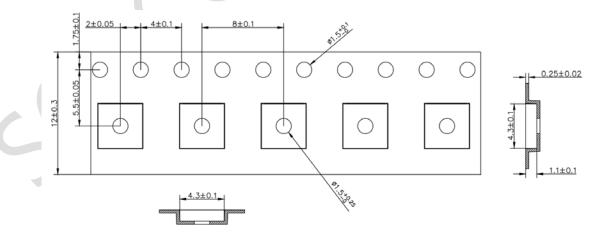

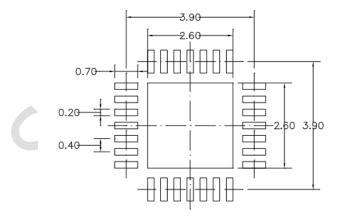

# PACKAGE INFORMATION

# PACKAGE OUTLINE DRAWING FOR 28L QFN (4.0X4.0MM) POD-0030 Revision 1.0

### **TOP VIEW**

**BOTTOM VIEW**

#### **SIDE VIEW**

#### **RECOMMENDED LAND PATTERN**

#### NOTE:

- 1) ALL DIMENSIONS ARE IN MILLIMETERS.

- 2) EXPOSED PADDLE SIZE DOES NOT INCLUDE MOLD FLASH.

- 3) LEAD COPLANARITY SHALL BE 0.08 MILLIMETERS MAX.

- 4) JEDEC REFERENCE IS MO-220.

- 5) DRAWING IS NOT TO SCALE.

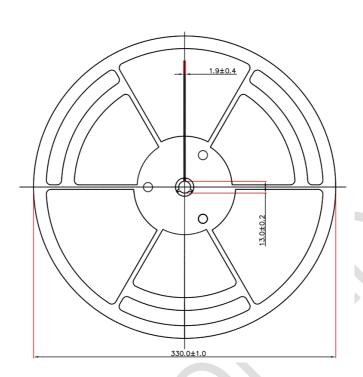

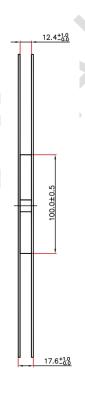

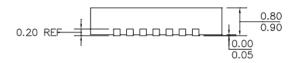

# TAPE AND REEL INFORMATION

| Orderable Device | Package Type | Pins | SPQ  |

|------------------|--------------|------|------|

| SCT55610QZAR     | QFN-28L      | 28   | 3000 |