# 4.5V-60V Vin, 5A, High Efficiency Asynchronous Step-down DCDC Converter

## **FEATURES**

- Wide Input Range: 4.5V-60V

- Up to 5A Continuous Output Current

- 0.8V ±1% Feedback Reference Voltage

- Integrated 80mΩ High-Side MOSFET

- Low Quiescent Current: 175uA

- Pulse Skipping Mode (PSM) in light load

- 130ns Minimum On-time

- Adjustable Soft-start Time

- Fixed Switching Frequency: 570KHz

- Precision Enable Threshold for Programmable Input Voltage Under-Voltage Lock Out Protection (UVLO) Threshold and Hysteresis

- Low Dropout Mode Operation

- Derivable Inverting Voltage Regulator

- Over-voltage and Over-Temperature Protection

- Available in an ESOP-8 Package

## APPLICATIONS

- 12-V, 24-V, 48-V Industry and Telecom Power System

- Industrial Automation and Motor Control

- Vehicle Accessories

## **DESCRIPTION**

The SCT2653 is 5A buck converter with wide input voltage, ranging from 4.5V to 60V, which integrates an  $80m\Omega$  high-side MOSFET. The SCT2653, adopting the peak current mode control, supports the Pulse Skipping Modulation (PSM) which assists the converter on achieving high efficiency at light load or standby condition.

The SCT2653 features fixed 570KHz switching frequency. The SCT2653 allows power conversion from high input voltage to low output voltage with a minimum 130ns on-time of high-side MOSFET.

The device offers adjustable soft start to prevent inrush current during the startup of output voltage ramping. The SCT2653 features external loop compensation to provide the flexibility to optimize either loop stability or loop response.

The SCT2653 provides cycle-by-cycle current limit, thermal shutdown protection, output over-voltage protection and input voltage under-voltage protection. The device is available in an 8-pin ESOP-8 package.

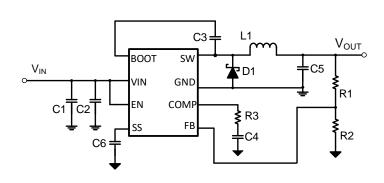

## TYPICAL APPLICATION

4.5V-60V, Asynchronous Buck Converter

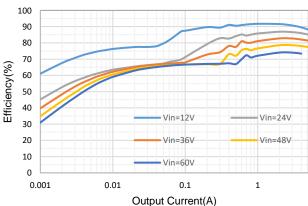

Efficiency, Vout=5V

1

## **REVISION HISTORY**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| Date      | Version | Revise                |

|-----------|---------|-----------------------|

| 2024/3/20 | 1.0     | Release to production |

## **DEVICE ORDER INFORMATION**

| PART NUMBER | PACKAGE MARKING | PACKAGE DISCRIPTION |  |

|-------------|-----------------|---------------------|--|

| SCT2653STE  | 2653            | ESOP-8              |  |

<sup>1)</sup> For Tape & Reel, Add Suffix R (e.g., SCT2653STER)

## **ABSOLUTE MAXIMUM RATINGS**

Over operating free-air temperature unless otherwise noted<sup>(1)</sup>

| DESCRIPTION                                      | MIN  | MAX | UNIT |

|--------------------------------------------------|------|-----|------|

| VIN, EN                                          | -0.3 | 65  | V    |

| BOOT                                             | -0.3 | 71  | V    |

| SW                                               | -1   | 65  | V    |

| BOOT-SW                                          | -0.3 | 6   | V    |

| COMP, FB, SS                                     | -0.3 | 6   | V    |

| Operating junction temperature TJ <sup>(2)</sup> | -40  | 150 | °C   |

| Storage temperature TSTG                         | -65  | 150 | °C   |

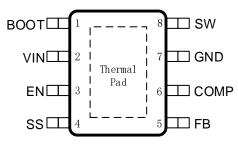

## **PIN CONFIGURATION**

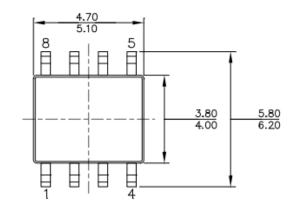

Figure 1. 8-Lead Plastic ESOP

## **PIN FUNCTIONS**

| NAME | NO. | PIN FUNCTION                                                                                                                                                                                                                                                                |

|------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| воот | 1   | Power supply bias for high-side power MOSFET gate driver. Connect a 0.1uF capacitor from BOOT pin to SW pin. Bootstrap capacitor is charged when SW voltage is low.                                                                                                         |

| VIN  | 2   | Input supply voltage. Connect a local bypass capacitor from VIN pin to GND pin. Path from VIN pin to high frequency bypass capacitor and GND must be as short as possible.                                                                                                  |

| EN   | 3   | Enable pin to the regulator with internal pull-up current source. Pull below 1.05V to disable the converter. Float or connect to VIN to enable the converter. The tap of resistor divider from VIN to GND connecting EN pin can adjust the input voltage lockout threshold. |

| SS   | 4   | Slow-start and Tracking. An external capacitor connected to this pin sets the output rise time. Since the voltage on this pin overrides the internal reference, it can be used for tracking and sequencing.                                                                 |

| FB   | 5   | Inverting input of the trans-conductance error amplifier. The tap of external feedback resistor divider from the output to GND sets the output voltage. The device regulates FB voltage to the internal reference value of 0.8V typical.                                    |

| COMP | 6   | Error amplifier output. Connect to frequency loop compensation network.                                                                                                                                                                                                     |

| GND  | 7   | Ground.                                                                                                                                                                                                                                                                     |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Rating may cause device permanent damage. The device is not guaranteed to function outside of its Recommended Operation Conditions.

<sup>(2)</sup> The IC includes over temperature protection to protect the device during overload conditions. Junction temperature will exceed 150°C when over temperature protection is active. Continuous operation above the specified maximum operating junction temperature will reduce lifetime.

| SW      | 8 | Regulator switching output. Connect SW to an external power inductor.                  |

|---------|---|----------------------------------------------------------------------------------------|

| Thermal | 9 | Heat dissipation path of die. Electrically connection to GND pin. Must be connected to |

| _Pad    |   | ground plane on PCB for proper operation and optimized thermal performance.            |

## RECOMMENDED OPERATING CONDITIONS

Over operating free-air temperature range unless otherwise noted

| PARAMETER | DEFINITION                     | MIN | MAX | UNIT |

|-----------|--------------------------------|-----|-----|------|

| Vin       | Input voltage range            | 4.5 | 60  | V    |

| Vout      | Output voltage range           | 0.8 | 57  | V    |

| TJ        | Operating junction temperature | -40 | 150 | °C   |

## **ESD RATINGS**

| PARAMETER | DEFINITION                                                                                    | MIN | MAX | UNIT |

|-----------|-----------------------------------------------------------------------------------------------|-----|-----|------|

|           | Human Body Model (HBM), per ANSI-JEDEC-JS-001-<br>2014 specification, all pins <sup>(1)</sup> | -3  | +3  | kV   |

| Vesd      | Charged Device Model (CDM), per ANSI-JEDEC-JS-002-2014 specification, all pins <sup>(2)</sup> | -1  | +1  | kV   |

<sup>(1)</sup> JEDEC document JEP155 states that 500V HBM allows safe manufacturing with a standard ESD control process.

## THERMAL INFORMATION

| PARAMETER            | THERMAL METRIC                                              | ESOP-8 | UNIT |

|----------------------|-------------------------------------------------------------|--------|------|

| R <sub>θJA</sub>     | Junction to ambient thermal resistance <sup>(1)</sup>       | 33.81  |      |

| $\Psi_{JT}$          | Junction-to-top characterization parameter                  | 4.7    |      |

| $\Psi_{JB}$          | Junction-to-board characterization parameter <sup>(1)</sup> | 13.44  | °C/W |

| R <sub>θ</sub> JCtop | Junction to case thermal resistance <sup>(1)</sup>          | 63.21  |      |

| Rejb                 | Junction-to-board thermal resistance <sup>(1)</sup>         | 13.89  |      |

<sup>(1)</sup> SCT provides  $R_{\theta JA}$  and  $R_{\theta JC}$  numbers only as reference to estimate junction temperatures of the devices.  $R_{\theta JA}$  and  $R_{\theta JC}$  are not a characteristic of package itself, but of many other system level characteristics such as the design and layout of the printed circuit board (PCB) on which the SCT2653 is mounted, thermal pad size, and external environmental factors. The PCB board is a heat sink that is soldered to the leads and thermal pad of the SCT2653. Changing the design or configuration of the PCB board changes the efficiency of the heat sink and therefore the actual  $R_{\theta JA}$  and  $R_{\theta JC}$ .

<sup>(2)</sup> JEDEC document JEP157 states that 250V CDM allows safe manufacturing with a standard ESD control process.

# **ELECTRICAL CHARACTERISTICS**

V<sub>IN</sub>=24V, T<sub>J</sub>=-40°C~125°C, typical value is tested under 25°C.

| SYMBOL                  | PARAMETER                                           | TEST CONDITION                                                  | MIN   | TYP        | MAX   | UNI     |

|-------------------------|-----------------------------------------------------|-----------------------------------------------------------------|-------|------------|-------|---------|

| Power Sup               | ply                                                 |                                                                 | 1     |            |       | •       |

| Vin                     | Operating input voltage                             |                                                                 | 4.5   |            | 60    | V       |

| VIN_UVLO                | Input UVLO Threshold Hysteresis                     | V <sub>IN</sub> rising                                          |       | 4.2<br>320 | 4.4   | V<br>mV |

| İshdn                   | Shutdown current from VIN pin                       | EN=0, no load                                                   |       | 2          | 5     | μA      |

| lα                      | Quiescent current from VIN pin                      | EN floating, no load, non-<br>switching, BOOT-SW=5V             | 175   |            |       | μA      |

| Power MOS               | SFETs                                               |                                                                 |       |            |       |         |

| R <sub>DSON_H</sub>     | High-side MOSFET on-resistance                      | V <sub>BOOT</sub> -V <sub>SW</sub> =5V                          |       | 80         |       | mΩ      |

| Reference               | and Control Loop                                    |                                                                 | •     |            |       |         |

| V <sub>REF</sub>        | Reference voltage of FB                             |                                                                 | 0.792 | 0.8        | 0.808 | V       |

| G <sub>EA</sub>         | Error amplifier trans-conductance                   | -2µA <i<sub>COMP&lt;2µA, V<sub>COMP</sub>=1V</i<sub>            | 1     | 92         |       | μS      |

| ICOMP_SRC               | EA maximum source current                           | V <sub>FB</sub> =V <sub>REF</sub> -100mV, V <sub>COMP</sub> =1V | 1     | 10         |       | μA      |

| <br>Icomp_snk           | EA maximum sink current                             | V <sub>FB</sub> =V <sub>REF</sub> +100mV, V <sub>COMP</sub> =1V |       | 10         |       | μA      |

| Av                      | Switch to COMP trans conductance                    |                                                                 | 20    |            | A/V   |         |

| V <sub>СОМР_Н</sub>     | COMP high clamp                                     |                                                                 | 2.25  |            | V     |         |

| <br>V <sub>СОМР_L</sub> | COMP low clamp                                      |                                                                 | 0.47  |            | V     |         |

| Current Lin             | nit and Over Current Protection                     |                                                                 |       |            |       |         |

| I <sub>LIM_HS</sub>     | High-side power MOSFET peak current limit threshold |                                                                 | 6.8   | 8          | 9.2   | А       |

| Enable and              | l Soft Startup                                      |                                                                 |       |            |       |         |

| V <sub>EN_H</sub>       | Enable high threshold                               |                                                                 |       | 1.2        |       | V       |

| V <sub>EN_L</sub>       | Enable low threshold                                |                                                                 |       | 1.05       |       | V       |

| I <sub>EN L</sub>       | Enable pin pull-up current                          | EN=1V                                                           |       | 1          |       | μA      |

| I <sub>EN_H</sub>       | Enable pin pull-up current                          | EN=1.5V                                                         |       | 4          |       | uA      |

| Iss                     | SS charge current                                   |                                                                 |       | 2          |       | uA      |

| Switching               | Frequency and External Clock Synchro                | onization                                                       |       |            |       |         |

| Fsw                     | Switching frequency                                 |                                                                 |       | 570        |       | kHz     |

| ton_min                 | Minimum on-time                                     | V <sub>IN</sub> =24V                                            |       | 130        |       | ns      |

| Protection              | 1                                                   |                                                                 | 1     |            |       | 1       |

|                         | Feedback overvoltage with respect to                | V <sub>FB</sub> /V <sub>REF</sub> rising                        |       | 110        |       | %       |

| V <sub>OVP</sub>        | reference voltage                                   | V <sub>FB</sub> /V <sub>REF</sub> falling                       |       | 105        |       | %       |

| V <sub>BOOTUV</sub>     | BOOT-SW UVLO threshold                              | BOOT-SW falling                                                 |       | 2.52       |       | V       |

| VUIUV                   |                                                     | Hysteresis                                                      |       | 230        |       | mV      |

| T <sub>SD</sub>         | Thermal shutdown threshold *                        | T <sub>J</sub> rising                                           |       | 172        |       | °C      |

|                         |                                                     | Hysteresis                                                      |       | 12         |       | °C      |

<sup>\*</sup>Derived from bench characterization

4 For more information <u>www.silicontent.com</u> © 2024 Silicon Content Technology Co., Ltd. All Rights Reserved

# TYPICAL CHARACTERISTICS

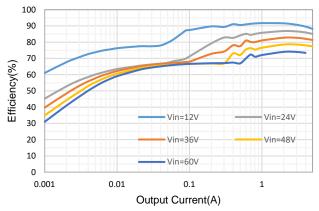

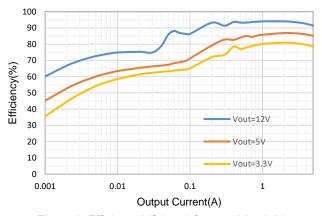

Figure 2. Efficiency VS Load Current, Vout=5V

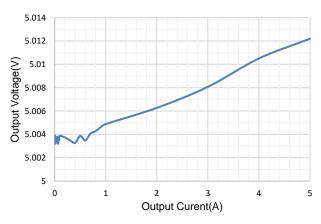

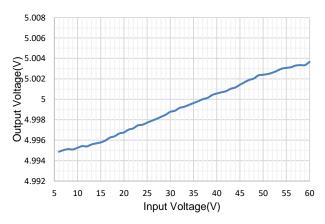

Figure 4. Load Regulation, Vin=24V, Vout=5V

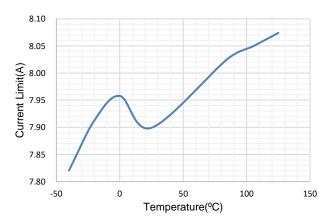

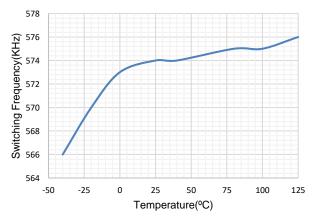

Figure 6. Current Limit VS Temperature

Figure 3. Efficiency VS Load Current, Vin=24V

Figure 5. Line Regulation, Vout=5V, lout=2.5A

Figure 7. Switching Frequency VS Temperature

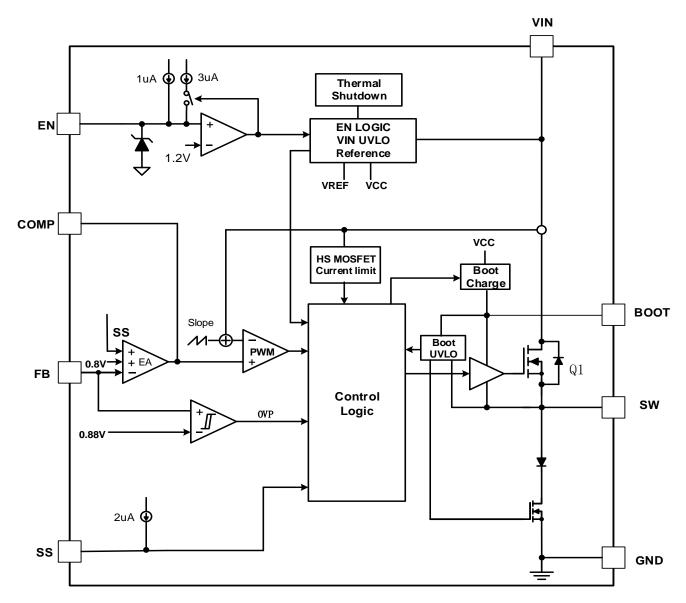

# **FUNCTIONAL BLOCK DIAGRAM**

Figure 8. Functional Block Diagram

## **OPERATION**

#### Overview

The SCT2653 is a 4.5V-60V input, 5A output, buck converter with integrated  $80m\Omega$  Rdson high-side power MOSFET. It implements constant frequency peak current mode control to regulate output voltage, providing excellent line and load transient response and simplifying the external loop compensation design.

The device also supports monolithic startup with pre-biased output condition. The seamless mode-transition between PWM mode and PSM mode operations ensure high efficiency over wide load current range. The quiescent current is typically 175uA under no load or sleep mode condition to achieve high efficiency at light load.

The SCT2653 has a default input start-up voltage of 4.2V with 320mV hysteresis. The EN pin is a high-voltage pin with a precision threshold that can be used to adjust the input voltage lockout thresholds with two external resistors to meet accurate higher UVLO system requirements. Floating EN pin enables the device with the internal pull-up current to the pin. Connecting EN pin to VIN directly starts up the device automatically.

The SCT2653 full protection features include the input under-voltage lockout, the output over-voltage protection, over current protection with cycle-by-cycle current limiting, output hard short protection and thermal shutdown protection.

## **Peak Current Mode Control**

The SCT2653 employs fixed frequency peak current mode control. An internal clock initiates turning on the integrated high-side power MOSFET Q1 in each cycle, then inductor current rises linearly. When the current through high-side MOSFET reaches the threshold level set by the COMP voltage of the internal error amplifier, the integrated high-side MOSFET is turned off.

The error amplifier serves the COMP node by comparing the voltage of the FB pin with an internal 0.8V reference voltage. When the load current increases, a reduction in the feedback voltage relative to the reference raises COMP voltage till the average inductor current matches the increased load current. This feedback loop well regulates the output voltage to the reference. The device also integrates an internal slope compensation circuitry to prevent subharmonic oscillation when duty cycle is greater than 50% for a fixed frequency peak current mode control.

The SCT2653 operates in Pulse Skipping Mode (PSM) with light load current to improve efficiency. When the load current decreases, an increment in the feedback voltage leads COMP voltage drop. When COMP falls to a low clamp threshold (470mV typically), device enters PSM. The output voltage decays due to output capacitor discharging during skipping period. Once FB voltage drops lower than the reference voltage, and the COMP voltage rises above low clamp threshold. Then high-side power MOSFET turns on in next clock pulse. After several switching cycles with typical 200mA peak inductor current, COMP voltage drops and is clamped again and pulse skipping mode repeats if the output continues light loaded.

This control scheme helps achieving higher efficiency by skipping cycles to reduce switching power loss and gate drive charging loss. The controller consumption quiescent current is 175uA during skipping period with no switching to improve efficiency further.

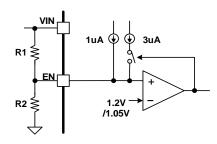

## **Enable and Under Voltage Lockout Threshold**

The SCT2653 is enabled when the VIN pin voltage rises above 4.2V and the EN pin voltage exceeds the enable threshold of 1.2V. The device is disabled when the VIN pin voltage falls below 3.88V or when the EN pin voltage is below 1.05V. An internal 1uA pull up current source to EN pin allows the device enable when EN pin floats.

EN pin is a high voltage pin that can be connected to VIN directly to start up the device.

For a higher system UVLO threshold, connect an external resistor divider (R1 and R2) shown in Figure 9 from VIN to EN. The UVLO rising and falling threshold can be calculated by Equation 1 and Equation 2 respectively.

$$R1 = \frac{V_{rise} * 0.875 - V_{fall}}{3.125uA} \tag{1}$$

$$R2 = \frac{R_1 \times 1.05}{V_{fall} - 1.05 + R_1 * 4uA} \tag{2}$$

where

- V<sub>rise</sub> is rising threshold of Vin UVLO

- V<sub>fall</sub> is falling threshold of Vin UVLO

Figure 9. System UVLO by enable divide

## **Output Voltage**

The SCT2653 regulates the internal reference voltage at 0.8V with  $\pm 1\%$  tolerance over the operating temperature and voltage range. The output voltage is set by a resistor divider from the output node to the FB pin. It is recommended to use 1% tolerance or better resistors. Use Equation 3 to calculate resistance of resistor dividers. To improve efficiency at light loads, larger value resistors are recommended. However, if the values are too high, the regulator will be more susceptible to noise affecting output voltage accuracy.

$$R_{FB\_TOP} = \left(\frac{V_{OUT}}{V_{REF}} - 1\right) * R_{FB\_BOT} \tag{3}$$

where

- R<sub>FB\_TOP</sub> is the resistor connecting the output to the FB pin.

- RFB BOT is the resistor connecting the FB pin to the ground.

## **Programmable Soft-Start**

The SCT2653 features programmable soft-start time to prevent inrush current during start-up stage. The soft-start time can be programmed easily by connecting a soft-start capacitor  $C_{ss}$  from SS pin to ground.

The SS pin sources an internal  $2\mu A$  current charging the external soft-start capacitor  $C_{ss}$  when the EN pin exceeds turn-on threshold. The device adopts the lower voltage between the internal voltage reference 0.8V and the SS pin voltage as the reference input voltage of the error amplifier and regulates the output. The soft-start completes when the voltage at the SS pin exceeds the internal reference voltage of 0.8V.

The soft-start capacitor value can be calculated going with following Equation 4. Attention should be taken here that the programmed soft-start time should be larger than 1ms.

$$C_{ss} = t_{ss} * \frac{2uA}{0.8V} \tag{4}$$

Where:

- Css is the soft-start capacitor connected from SS pin to the ground

- t<sub>ss</sub> is the soft-start time

## **Bootstrap Voltage Regulator and Low Drop-out Operation**

An external bootstrap capacitor between BOOT pin and SW pin powers the floating gate driver to high-side power MOSFET. The bootstrap capacitor voltage is charged from an integrated voltage regulator when high-side power MOSFET is off and the external low-side diode conducts. The recommended value of the BOOT capacitor is 0.1 µF.

The UVLO of high-side MOSFET gate driver has rising threshold of 2.52V and hysteresis of 230mV. When the device operates with high duty cycle or extremely light load, bootstrap capacitor may be not recharged in

considerable long time. The voltage at bootstrap capacitor is insufficient to drive high-side MOSFET fully on. When the voltage across bootstrap capacitor drops below 2.29V, BOOT UVLO occurs. The converter forces turning on an integrated low-side MOSFET periodically to refresh the voltage of bootstrap capacitor to guarantee the converter's operation over a wide duty range.

During the condition of ultra-low voltage difference from the input to the output, SCT2653 operates in Low Drop-Out LDO mode. High-side MOSFET remains turning on as long as the BOOT pin to SW pin voltage is higher than BOOT UVLO threshold 2.52V. When the voltage from BOOT to SW drops below 2.29V, the high-side MOSFET turns off and low-side MOSFET turns on to recharge bootstrap capacitor periodically in the following several switching cycles. Low-side MOSFET only turns on for 100ns in each refresh cycle to minimize the output voltage ripple. Low-side MOSFET may turn on for several times till the bootstrap voltage is charged to higher than 2.52V for high-side MOSFET working normally. The effective duty cycle of the converter during LDO operation can be approaching to 100%.

During slowing power up and power down application, the output voltage can closely track the input voltage ramping down thanks to LDO operation mode. As the input voltage is reduced to near the output voltage, i.e., during slowing power-up and power-down application, the off-time of the high side MOSFET starts to approach the minimum value. Without LDO operation mode, beyond this point the switching may become erratic and/or the output voltage will fall out of regulation. To avoid this problem, the SCT2653 LDO mode automatically reduces the switching frequency to increase the effective duty cycle and maintain regulation.

#### **Over Current Limit**

The SCT2653 implements over current protection with fold back current limit. The SCT2653 cycle-by-cycle limits high-side MOSFET peak current to avoid inductor current running away during unexpected overload or output hard short condition.

When overload or hard short happens, the converter cannot provide output current to satisfy loading requirement. The inductor current is clamped at over current limitation. Thus, the output voltage drops below regulated voltage with FB voltage less than internal reference voltage continuously. The COMP pin voltage ramps up to high clamp voltage 2.25V typical.

The SCT2653 implements frequency foldback to protect the converter in unexpected overload or output hard short condition at higher switching frequencies and input voltages. The oscillator frequency is divided by 1, 2, 4, and 8 as the FB pin voltage falls from 0.8 V to 0 V. The SCT2653 uses a digital frequency foldback to enable synchronization to an external clock during normal start-up and fault conditions. During short-circuit events, the inductor current can exceed the peak current limit because of the high input voltage and the minimum on-time. When the output voltage is forced low by the shorted load, the inductor current decreases slowly during the switch off-time. The frequency foldback effectively increases the off-time by increasing the period of the switching cycle providing more time for the inductor current to ramp down.

With a maximum frequency foldback ratio of 8, there is a maximum frequency at which the inductor current can be controlled by frequency foldback protection. Equation 5 calculates the maximum switching frequency at which the inductor current remains under control when  $V_{\text{OUT}}$  is forced to  $V_{\text{OUT\_SHORT}}$ . The selected operating frequency must not exceed the calculated value.

$$f_{sw(\max skip)} = \frac{f_{DIV}}{t_{min\_oN}} \times \left(\frac{I_{LIMIT} \times R_{DC} + V_{OUT\_SHORT} + V_d}{V_{IN\_MAX} - I_{LIMIT} \times R_{DS(on)} + V_d}\right)$$

(5)

where

$I_{LIMIT}$ : Limited average current  $R_{DC}$ : Inductor DC resistance

$V_{IN\_MAX}$ : Maximum input voltage

*V<sub>OUT SHORT</sub>*: Output voltage during short

$V_d$ : Diode voltage drop

## **SCT2653**

R<sub>DS(on)</sub>: Integrated high side FET on resistance

$T_{min\_ON}$ : Controllable minimum on time

$f_{DIV}$ : Frequency divide equals (1,2,4 or 8)

## **Over voltage Protection**

The SCT2653 implements the Over-voltage Protection OVP circuitry to minimize output voltage overshoot during load transient, recovering from output fault condition or light load transient. The overvoltage comparator in OVP circuit compares the FB pin voltage to the internal reference voltage. When FB voltage exceeds 110% of internal 0.8V reference voltage, the high-side MOSFET turns off to avoid output voltage continue to increase. When the FB pin voltage falls below 105% of the 0.8V reference voltage, the high-side MOSFET can turn on again.

## **Thermal Shutdown**

The SCT2653 protects the device from the damage during excessive heat and power dissipation conditions. Once the junction temperature exceeds 172°C, the internal thermal sensor stops power MOSFETs switching. When the junction temperature falls below 160°C, the device restarts with internal soft start phase.

For more information www.silicontent.com © 2024 Silicon Content Technology Co., Ltd. All Rights Reserved

## APPLICATION INFORMATION

## **Typical Application**

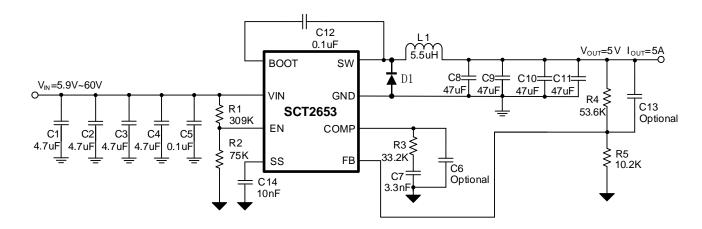

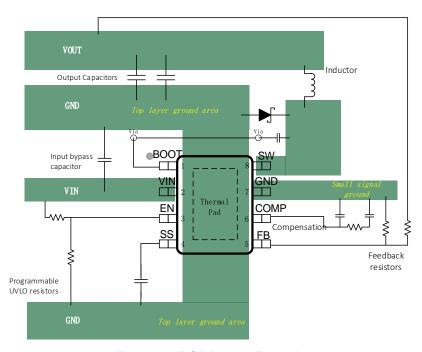

Figure 10. SCT2653 Design Example, 5V Output with Programmable UVLO

**Design Parameters**

| Design Parameters                           | Example Value          |

|---------------------------------------------|------------------------|

| Input Voltage                               | 24V Normal 5.9V to 60V |

| Output Voltage                              | 5V                     |

| Maximum Output Current                      | 5A                     |

| Switching Frequency                         | 570 KHz                |

| Output voltage ripple (peak to peak)        | 3.16mV                 |

| Transient Response 1.25A to 3.75A load step | ∆Vout = 452mV          |

| Start Input Voltage (rising VIN)            | 5.9V                   |

| Stop Input Voltage (falling VIN)            | 4.5V                   |

## **Output Voltage**

The output voltage is set by an external resistor divider  $R_4$  and  $R_5$  in typical application schematic. Recommended  $R_5$  resistance is 10.2K $\Omega$ . Use Equation 6 to calculate  $R_4$ .

$$R_4 = \left(\frac{V_{OUT}}{V_{REF}} - 1\right) * R_5 \tag{6}$$

where:

V<sub>REF</sub> is the feedback reference voltage, typical 0.8V

Table 1. R4, R5 Value for Common Output Voltage (Room Temperature)

| <b>V</b> out | R <sub>4</sub> | R₅      |

|--------------|----------------|---------|

| 3.3 V        | 31.6 ΚΩ        | 10.2 ΚΩ |

| 5 V          | 53.6 KΩ        | 10.2 ΚΩ |

| 12 V         | 143 ΚΩ         | 10.2 ΚΩ |

| 24 V         | 294 ΚΩ         | 10.2 ΚΩ |

| 36 V         | 442 KΩ         | 10.2 ΚΩ |

## **Under Voltage Lock-Out**

An external voltage divider network of  $R_1$  from the input to EN pin and  $R_2$  from EN pin to the ground can set the input voltage's Under Voltage Lock-Out (UVLO) threshold. The UVLO has two thresholds, one for power up when the input voltage is rising and the other for power down or brown outs when the input voltage is falling. For the example design, the supply should turn on and start switching once the input voltage increases above 5.9V (start or enable). After the regulator starts switching, it should continue to do so until the input voltage falls below 4.5 V (stop or disable). Use Equation 7 and Equation 8 to calculate the values 309 k $\Omega$  and 75 k $\Omega$  of  $R_1$  and  $R_2$  resistors.

$$R_1 = \frac{V_{rise} * 0.875 - V_{fall}}{3.125uA} \tag{7}$$

$$R_2 = \frac{R_1 \times 1.05}{V_{fall} - 1.05 + R_1 * 4uA} \tag{8}$$

## **Inductor Selection**

There are several factors should be considered in selecting inductor such as inductance, saturation current, the RMS current and DC resistance (DCR). Larger inductance results in less inductor current ripple and therefore leads to lower output voltage ripple. However, the larger value inductor always corresponds to a bigger physical size, higher series resistance, and lower saturation current. A good rule for determining the inductance to use is to allow the inductor peak-to-peak ripple current to be approximately 20%~40% of the maximum output current.

The peak-to-peak ripple current in the inductor ILPP can be calculated as in Equation 9.

$$I_{LPP} = \frac{V_{OUT} * (V_{IN} - V_{OUT})}{V_{IN} * L * f_{SW}}$$

(9)

Where

- ILPP is the inductor peak-to-peak current

- · L is the inductance of inductor

- fsw is the switching frequency

- V<sub>OUT</sub> is the output voltage

- V<sub>IN</sub> is the input voltage

Since the inductor-current ripple increases with the input voltage, so the maximum input voltage in application is always used to calculate the minimum inductance required. Use Equation 10 to calculate the inductance value.

$$L_{MIN} = \frac{V_{OUT}}{f_{SW} * LIR * I_{OUT(max)}} * (1 - \frac{V_{OUT}}{V_{IN(max)}})$$

(10)

#### Where

- L<sub>MIN</sub> is the minimum inductance required

- f<sub>sw</sub> is the switching frequency

- V<sub>OUT</sub> is the output voltage

- V<sub>IN(max)</sub> is the maximum input voltage

- IOUT(max) is the maximum DC load current

- LIR is coefficient of ILPP to IOUT

The total current flowing through the inductor is the inductor ripple current plus the output current. When selecting an inductor, choose its rated current especially the saturation current larger than its peak operation current and RMS current also not be exceeded. Therefore, the peak switching current of inductor, ILPEAK and ILRMS can be calculated as in Equation 11 and Equation 12.

$$I_{LPEAK} = I_{OUT} + \frac{I_{LPP}}{2} \tag{11}$$

$$I_{LPEAK} = I_{OUT} + \frac{I_{LPP}}{2}$$

$$I_{LRMS} = \sqrt{(I_{OUT})^2 + \frac{1}{12} * (I_{LPP})^2}$$

(11)

## Where

- I<sub>LPEAK</sub> is the inductor peak current

- lout is the DC load current

- ILPP is the inductor peak-to-peak current

- ILRMS is the inductor RMS current

In overloading or load transient conditions, the inductor peak current can increase up to the switch current limit of the device which is typically 8A. The most conservative approach is to choose an inductor with a saturation current rating greater than 8A. Because of the maximum I<sub>LPEAK</sub> limited by device, the maximum output current that the SCT2653 can deliver also depends on the inductor current ripple. Thus, the maximum desired output current also affects the selection of inductance. The smaller inductor results in larger inductor current ripple leading to a lower maximum output current.

#### **Diode Selection**

The SCT2653 requires an external catch diode between the SW pin and GND. The selected diode must have a reverse voltage rating equal to or greater than VIN (max). The peak current rating of the diode must be greater than the maximum inductor current. Schottky diodes are typically a good choice for the catch diode due to their low forward voltage. The lower the forward voltage of the diode, the higher the efficiency of the regulator.

Typically, diodes with higher voltage and current ratings have higher forward voltages. A diode with a minimum of 60-V reverse voltage is preferred to allow input voltage transients up to the rated voltage of the SCT2653.

For the example design, the PDS760-13 Schottky diode is selected for its lower forward voltage and good thermal characteristics compared to smaller devices. The typical forward voltage of the PDS760-13 is 0.52V at 5A.

The diode must also be selected with an appropriate power rating. The diode conducts the output current during the off-time of the internal power switch. The off-time of the internal switch is a function of the maximum input voltage, the output voltage, and the switching frequency. The output current during the off-time is multiplied by the forward voltage of the diode to calculate the instantaneous conduction losses of the diode. At higher switching frequencies, the ac losses of the diode need to be taken into account. The ac losses of the diode are due to the charging and discharging of the junction capacitance and reverse recovery charge. Equation 14 is used to calculate the total power dissipation, including conduction losses and ac losses of the diode.

The PDS760-13 diode has a junction capacitance of 400pF. Using Equation 13, the total loss in the diode at the maximum input voltage is 2.45 W.

## **SCT2653**

If the power supply spends a significant amount of time at light load currents or in sleep mode, consider using a diode which has a low leakage current and slightly higher forward voltage drop.

$$P_{D} = \frac{(V_{IN\_MAX} - V_{OUT}) \times I_{OUT} \times V_{d}}{V_{IN\_MAX}} + \frac{C_{j} \times f_{SW} \times (V_{IN} + V_{d})^{2}}{2}$$

(13)

## **Input Capacitor Selection**

The input current to the step-down DCDC converter is discontinuous, therefore it requires a capacitor to supply the AC current to the step-down DCDC converter while maintaining the DC input voltage. Use capacitors with low ESR for better performance. Ceramic capacitors with X5R or X7R dielectrics are usually suggested because of their low ESR and small temperature coefficients, and it is strongly recommended to use another lower value capacitor (e.g., 0.1uF) with small package size (0603) to filter high frequency switching noise. Place the small size capacitor as close to VIN and GND pins as possible.

The voltage rating of the input capacitor must be greater than the maximum input voltage. And the capacitor must also have a ripple current rating greater than the maximum input current ripple. The RMS current in the input capacitor can be calculated using Equation 14.

$$I_{CINRMS} = I_{OUT} * \sqrt{\frac{V_{OUT}}{V_{IN}} * (1 - \frac{V_{OUT}}{V_{IN}})}$$

(14)

The worst-case condition occurs at  $V_{IN}=2*V_{OUT}$ , where:

$$I_{CINRMS} = 0.5 * I_{OUT} \tag{15}$$

For simplification, choose an input capacitor with an RMS current rating greater than half of the maximum load current.

When selecting ceramic capacitors, it needs to consider the effective value of a capacitor decreasing as the DC bias voltage across a capacitor increasing.

The input capacitance value determines the input ripple voltage of the regulator. The input voltage ripple can be calculated using Equation 16 and the maximum input voltage ripple occurs at 50% duty cycle.

$$\Delta V_{IN} = \frac{I_{OUT}}{f_{SW} * C_{IN}} * \frac{V_{OUT}}{V_{IN}} * (1 - \frac{V_{OUT}}{V_{IN}})$$

(16)

For this example, four 4.7µF, X7R ceramic capacitors rated for 100 V in parallel are used. And a 0.1µF for high-frequency filtering capacitor is placed as close as possible to the device pins.

## **Bootstrap Capacitor Selection**

A  $0.1\mu F$  ceramic capacitor must be connected between BOOT pin and SW pin for proper operation. A ceramic capacitor with X5R or better grade dielectric is recommended. The capacitor should have a 10V or higher voltage rating.

## **Output Capacitor Selection**

The selection of output capacitor will affect output voltage ripple in steady state and load transient performance.

The output ripple is essentially composed of two parts. One is caused by the inductor current ripple going through the Equivalent Series Resistance ESR of the output capacitors and the other is caused by the inductor current ripple charging and discharging the output capacitors. To achieve small output voltage ripple, choose a low-ESR output capacitor like ceramic capacitor. For ceramic capacitors, the capacitance dominates the output ripple. For simplification, the output voltage ripple can be estimated by Equation 17 desired.

SCT

$$\Delta V_{OUT} = \frac{V_{OUT} * (V_{IN} - V_{OUT})}{8 * f_{SW}^2 * L * C_{OUT} * V_{IN}}$$

(17)

Where

- ΔV<sub>OUT</sub> is the output voltage ripple

- fsw is the switching frequency

- · L is the inductance of inductor

- Cout is the output capacitance

- V<sub>OUT</sub> is the output voltage

- V<sub>IN</sub>is the input voltage

Due to capacitor's degrading under DC bias, the bias voltage can significantly reduce capacitance. Ceramic capacitors can lose most of their capacitance at rated voltage. Therefore, leave margin on the voltage rating to ensure adequate effective capacitance. Typically, four 47µF ceramic output capacitors work for most applications.

## **Compensation Components**

The SCT2653 employs peak current mode control for easy compensation and fast transient response. An external network comprising resister R<sub>3</sub>, ceramic capacitors C<sub>7</sub> and optional C<sub>6</sub> connected to the COMP pin is used for the loop compensation. The Equation 18 shows the close-loop small signal transfer function.

$$H(S) = \left[ A_{EA} * \frac{1 + \frac{S}{2\pi * f_{Z1}}}{\left(1 + \frac{S}{2\pi * f_{P1}}\right) * \left(1 + \frac{S}{2\pi * f_{P2}}\right)} \right] * \left[ G_{ISNS} * \frac{V_{OUT}}{I_{OUT}} * \frac{1 + \frac{S}{2\pi * f_{Z2}}}{1 + \frac{S}{2\pi * f_{P2}}} \right] * \frac{V_{FB}}{V_{OUT}}$$

$$(18)$$

where

- A<sub>EA</sub> is error amplifier voltage gain

- GISNS is COMP to SW current trans-conductance, 17A/V typically

The DC voltage gain of the loop is given by Equation 19.

$$A_{VDC} = A_{EA} * G_{ISNS} * \frac{V_{FB}}{I_{OUT}} \tag{19}$$

The system has two noteworthy poles: one is due to the compensation capacitor C<sub>7</sub> and the error amplifier output resistor. The other is caused by the output capacitor and the load resistor. These poles as located at:

$$f_{P1} = \frac{1}{2\pi * R_{OEA} * C_7} = \frac{G_{EA}}{2\pi * A_{EA} * C_7}$$

(20)

$$f_{P2} = \frac{1}{2\pi * R_{LOAD} * C_{OUT}} = \frac{I_{OUT}}{2\pi * V_{OUT} * C_{OUT}}$$

(21)

where

- ROEA is error amplifier output resistor

- GEA is Error amplifier trans-conductance, 300uS typically

- R<sub>LOAD</sub> is equivalent load resistor

The system has one zero of importance from R<sub>3</sub> and C<sub>7</sub>. f<sub>z1</sub> is used to counteract the f<sub>p2</sub>, and f<sub>z1</sub> located at:

$$f_{Z1} = \frac{1}{2\pi * C_7 * R_2} \tag{22}$$

The system may have another important zero if the output capacitor has a large capacitance or a high ESR value. The zero, due to the ESR and the capacitance of the output capacitor is calculated by Equation 23.

$$f_{Z2} = \frac{1}{2\pi * C_{OUT} * ESR} \tag{23}$$

In this case, a third pole set by the optional compensation capacitor  $C_6$  and the compensation resistor  $R_3$  is used to compensates the effect of the ESR zero. This pole is calculated by Equation 24.

$$f_{P3} = \frac{1}{2\pi * C_6 * R_3} \tag{24}$$

The crossover frequency of converter is shown in Equation 25.

$$f_C = \frac{V_{FB}}{V_{OUT}} * \frac{G_{EA} * G_{ISNS} * R_3}{2\pi * C_{OUT}}$$

(25)

The system crossover frequency, where the feedback loop has unity gain, is important. A lower crossover frequency results in slower line and load transient response. A higher crossover frequency could cause the system unstable. A recommended rule of thumb is to set the crossover frequency to be approximately 1/10 of switching frequency.

The following steps can be followed to calculate the external compensation components. Calculate the compensation resistor R<sub>3</sub> with Equation 26 once crossover frequency is selected.

$$R_3 = \frac{V_{OUT}}{V_{FB}} * \frac{2\pi * C_{OUT} * f_C}{G_{EA} * G_{ISNS}}$$

(26)

Then calculate C<sub>7</sub> by placing a compensation zero at or before the output stage pole.

$$C_7 = \frac{R_{LOAD} * C_{OUT}}{R_3} \tag{27}$$

Determine if the optional compensation capacitor  $C_6$  is required. Generally, it is required if the ESR zero  $f_{Z2}$  is located less than half of the switching frequency. Then  $f_{p3}$  can be used to cancel  $f_{z2}$ .  $C_6$  can be calculated with Equation 28.

$$C_6 = \frac{C_{OUT} \times ESR}{R_3} \tag{28}$$

Table 2 lists typical values of compensation components for some standard output voltages with various output ceramic capacitors and inductors. The values of the compensation components have been optimized for fast transient responses and good stability. For the conditions do not list in Table 2, customers can use Equation 26-Equation 28 to optimize the compensation components.

Table 2: Compensation Values for Typical Output Voltage/Capacitor Combinations

| Vout | L1    | COUT   | R3    | C7     | C6              |

|------|-------|--------|-------|--------|-----------------|

| 3.3V | 5.5uH | 4*47uF | 20K   | 4.7 nF | 47pF (optional) |

| 5V   | 5.5uH | 4*47uF | 33.2K | 3.3nF  | 22pF (optional) |

| 12V  | 10uH  | 4*47uF | 53.6K | 1.8nF  | 100pF           |

| 24V  | 15uH  | 4*47uF | 105k  | 1nF    | 220pF           |

SCT

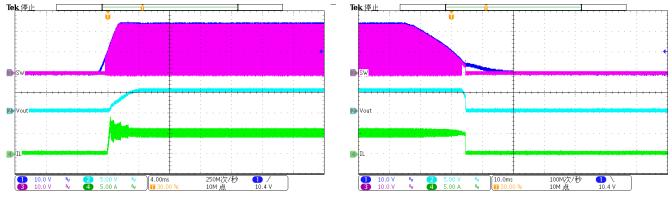

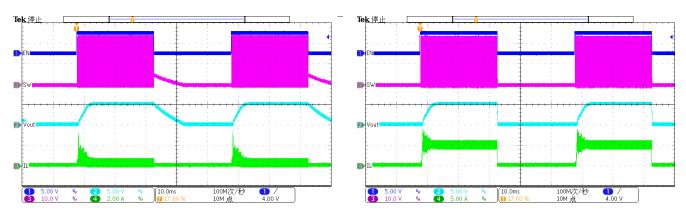

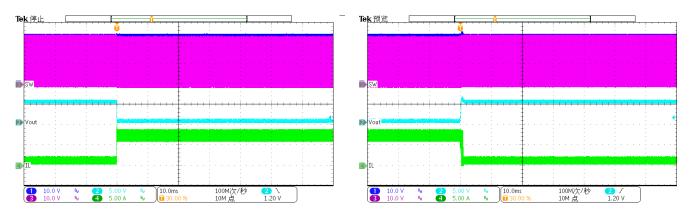

## **Application Waveforms**

V<sub>IN</sub>=24V, V<sub>OUT</sub>=5V, unless otherwise noted

Figure 11. Power up (ILOAD=5A)

Figure 12. Power down (ILOAD=5A)

Figure 13. EN toggle (I<sub>LOAD</sub>=0.1A)

Figure 14. EN toggle (I<sub>LOAD</sub>=5A)

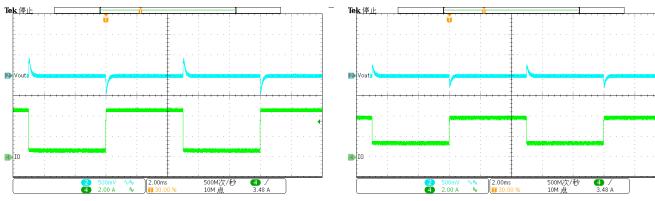

Figure 15. Over Current Protection (1A to hard short)

Figure 16. Over Current Release (hard short to 1A)

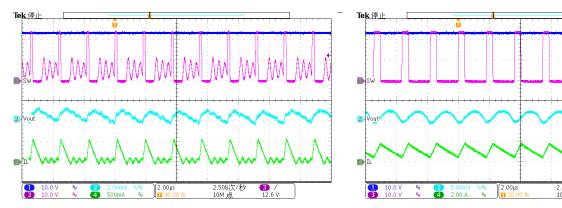

## **Application Waveforms**

Figure 17. Load Transient (0.5A-4.5A, 1.6A/us)

Figure 18. Load Transient (1.25A-3.75A, 1.6A/us)

Figure 19. Output Ripple (ILOAD=100mA)

Figure 20. Output Ripple (I<sub>LOAD</sub>=1A)

Figure 21. Output Ripple (I<sub>LOAD</sub>=5A)

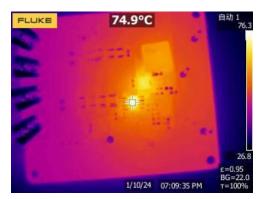

Figure 22. Thermal,  $24V_{IN}$ ,  $5V_{OUT}$ , 3A

## **Layout Guideline**

Proper PCB layout is a critical for SCT2653's stable and efficient operation. The traces conducting fast switching currents or voltages are easy to interact with stray inductance and parasitic capacitance to generate noise and degrade performance. For better results, follow these guidelines as below:

- 1. Power grounding scheme is very critical because of carrying power, thermal, and glitch/bouncing noise associated with clock frequency. The thumb of rule is to make ground trace lowest impendence and power are distributed evenly on PCB. Sufficiently placing ground area will optimize thermal and not causing overheat area.

- 2. Place a low ESR ceramic capacitor as close to VIN pin and the ground as possible to reduce parasitic effect.

- 3. Freewheeling diode should be place as close to SW pin and the ground as possible to reduce parasitic effect.

- 4. For operation at full rated load, the top side ground area must provide adequate heat dissipating area. Make sure top switching loop with power have lower impendence of grounding.

- 5. The bottom layer is a large ground plane connected to the ground plane on top layer by vias. The power pad should be connected to bottom PCB ground planes using multiple vias directly under the IC. The center thermal pad should always be soldered to the board for mechanical strength and reliability, using multiple thermal vias underneath the thermal pad. Improper soldering thermal pad to ground plate on PCB will cause SW higher ringing and overshoot besides downgrading thermal performance. it is recommended 10mil diameter drill holes of thermal vias, but a smaller via offers less risk of solder volume loss. On applications where solder volume loss thru the vias is of concern, plugging or tenting can be used to achieve a repeatable process.

- 6. Output inductor and freewheeling diode should be placed close to the SW pin. The switching area of the PCB conductor minimized to prevent excessive capacitive coupling.

- 7. UVLO adjust resistors and SS capacitor, loop compensation and feedback components should connect to small signal ground which must return to the GND pin without any interleaving with power ground.

- 8. Route BOOT capacitor trace on the other layer than top layer to provide wide path for topside ground.

- 9. For achieving better thermal performance, a four-layer layout is strongly recommended.

Figure 23. PCB Layout Example

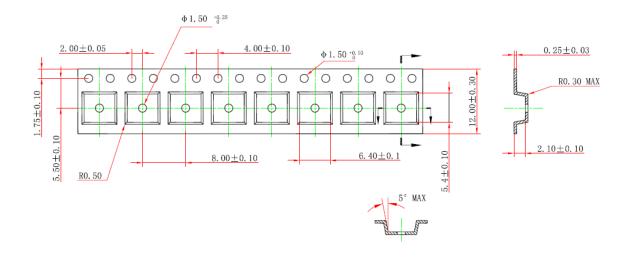

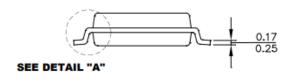

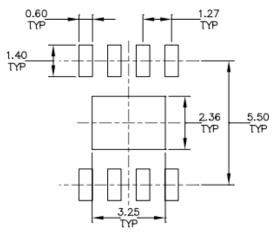

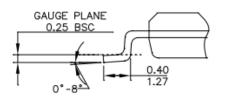

## PACKAGE INFORMATION

## **TOP VIEW**

#### **BOTTOM VIEW**

## **FRONT VIEW**

SIDE VIEW

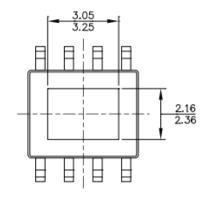

## RECOMMENDED LAND PATTERN

DETAIL "A"

## NOTE:

- 1) CONTROL DIMENSION IS IN INCHES. DIMENSION IN BRACKET IS IN MILLIMETERS.

- 2) PACKAGE LENGTH DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS.

- 3) PACKAGE WIDTH DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSIONS.

- 4) LEAD COPLANARITY (BOTTOM OF LEADS AFTER FORMING) SHALL BE 0.004" INCHES MAX.

- 5) DRAWING REFERENCE TO JEDEC MS-012, VARIATION AA.

- 6) DRAWING IS NOT TO SCALE.

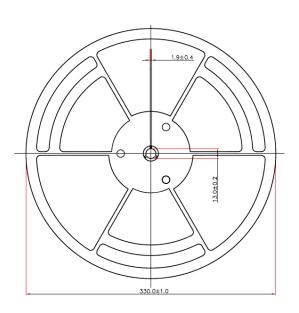

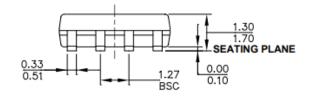

# TAPE AND REEL INFORMATION

| Orderable Device | Package Type | Pins | SPQ  |

|------------------|--------------|------|------|

| SCT2653STER      | ESOP         | 8    | 4000 |